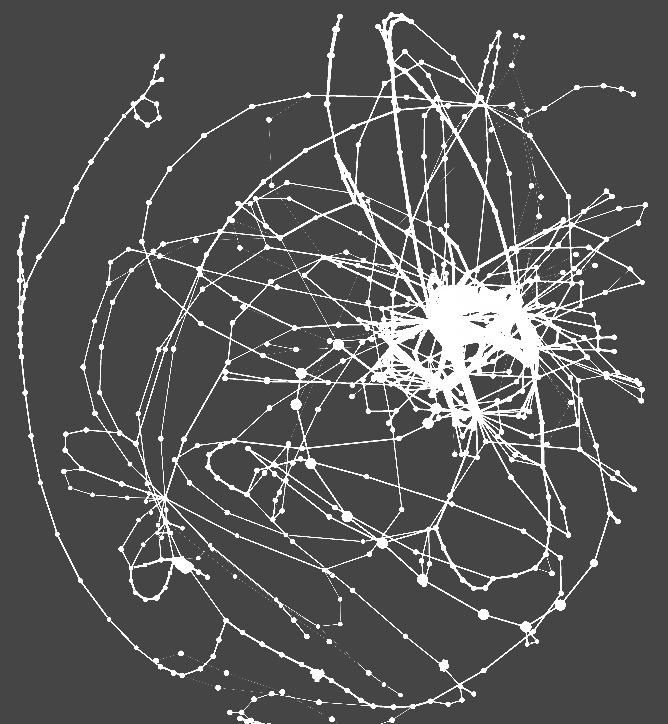

The PL241-Compiler is an SSA-based optimizing compiler that supports copy propagation, common subexpression elimination, constant folding, register allocation and code generation for the DLX (pronounced ‘Deluxe’) RISC processor architecture.

I wrote the compiler as a part of a graduate course at UC Irvine. It was both a challenging and extremely useful course and compiler to work on. In fact, I ended up borrowing ideas like value-numbering that are pivotal to the SSA-form for my own research projects. I would highly recommend this course to anyone who might be interested in, or is working on program analysis.

Essentially, I decided to open source the code of my implementation and continue working on it during my free time — yes, it is that interesting and addictive!

Tags:

Related Posts

- 02 May 2020 » Santa Monica Views

- 26 Apr 2020 » California, USA

- 04 Nov 2019 » Fall And Fires